点击空白处退出提示

作品详情

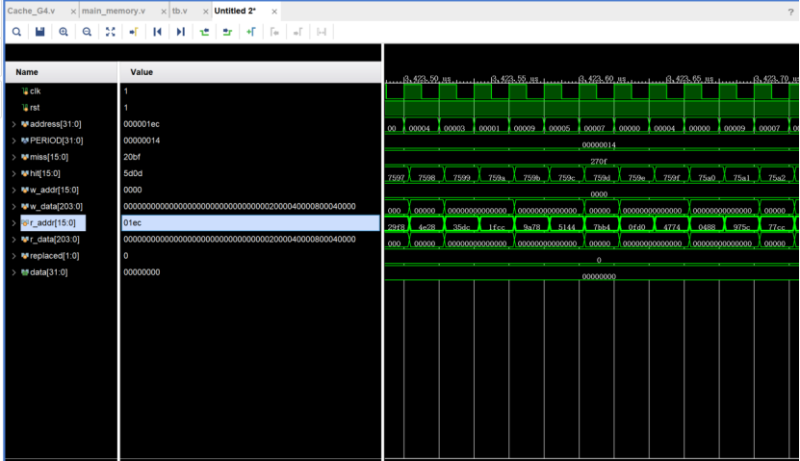

仿真环境:Vivado(2018.3 版本)

设计级别:行为级

采用直接映射、四路组相联映射方式设计 32 位高速缓存,采用Vivado 提供的 ip 核 BRAM 作为高速缓存的存储,完成了仿真,以 gcc 编译出的程序运行时的内存访问地址作为检验标准,对其分别统计命中率以反映不同映射方式的区别和效果。

声明:本文仅代表作者观点,不代表本站立场。如果侵犯到您的合法权益,请联系我们删除侵权资源!如果遇到资源链接失效,请您通过评论或工单的方式通知管理员。未经允许,不得转载,本站所有资源文章禁止商业使用运营!

评论