********

******** ********

********工作经历

2013-03-01 -2014-03-01富士通半导体IC设计工程师

负责把MATLAB算法转成Verilog表示的硬件实现,完成DVB-T2数字电视芯片SOC系统的多个模块设计和验证工作,以及FPGA原型验证平台的开发、测试和维护。

教育经历

2011-09-01 - 2012-09-01南安普顿大学芯片系统硕士

2006-09-01 - 2010-09-01桂林电子科技大学微电子学本科

技能

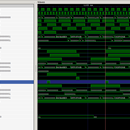

在个人博客上发布一个画时序图的小工具,起了个名字叫KWSequence,但是因为很忙(懒)所以页面建好后就一直挂在那里。半年以后我从同事那里看到了AndyTiming,惊奇的发现这个小工具的功能跟我设计的思路差不多,唯一不喜欢的地方就是支持的功能还不够多,画的图不够好看,可以配置的设置也不够多,而且只有windows系统支持,必须安装才能使用。于是,趁这几天不忙,我花了一天的时间,把AndyTiming的功能都用JS重新写了一遍并匆匆将功能上线了。 本工具是使用ASCII字符进行绘图的,脚本会自动检测字符画的内容变化并实时对绘图进行修改,实际测试结果我还是很满意的,可以说比手动画图效率高了几十倍,但是学习门槛又非常低。 开源地址:https//github.com/kellenwang1017/KWSequence

负责架构设计和主要模块设计及验证工作,ZYNQ和非ZYNQ的项目都做过,支持BD+GPS,用Verilog/SpinalHDL写代码都可以,仿真工具用过VCS/ Verilator/ QuestaSim/ ModelSim等等,主要做的都是Xilinx系列的FPGA